Лингвистические средства проектирования

Курс "Лингвистические средства проектирования" читается студентам 4 курса института ИнЭл, обучающимся по профилю "Интегральная электроника и наноэлектроника" (группы ЭН-41, ЭН-42, ЭН-43) в восьмом (весеннем) семестре.

План курса:

- 10 лекций;

- 5 лабораторных работ;

Самостоятельная работа к лекциям не предусмотрена

Изучение дисцины "Лингвистические средства САПР" заканчивается зачётом.

КРАТКАЯ АННОТАЦИЯ

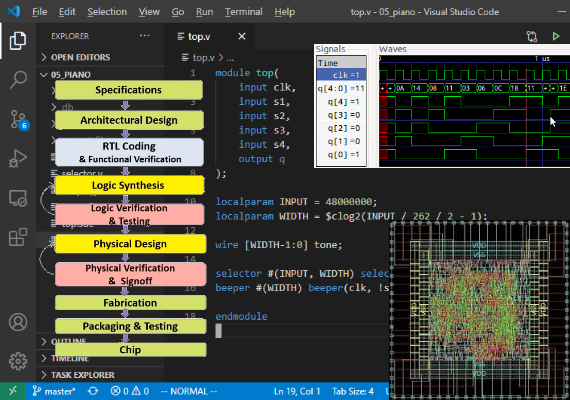

Лекционный материал предусматривает изучение назначения и синтаксических конструкций языка Verilog HDL, позволяющих описывать схемы на различных уровнях абстракции. Приводятся примеры использования параллельных и последовательных конструкций языка, операторов генерации. Даётся краткое сравнение языков Verilog HDL и VHDL.

Лабораторные работы посвящены разработке описания комбинационных и последовательностных схем.

Материалы к лекциям

Тематика лабораторных работ

Все лабораторные работы выполняются в лабораториях ВЦ МИЭТ в ОС Windows с использованием виртуальных машин.

| Лабораторная работа | Рассматриваемые вопросы | Материалы |

|---|---|---|

Задание 1 |

Знакомство со средой проектирования. Моделирование простых комбинационных вентилей. Временное и функциональное моделирование. Образ виртуальной машины доступен по ссылке. Сделал для вас краткое описание того, как работать с виртуальной машиной. Задание: для каждого из элементов представить описание и тестовое окружение, показать результаты моделирования, иллюстрирующие корректность описания. Файлы для синтеза:

Важно:

|

|

Задание 2 |

Описание и моделирование комбинационных схем. Задание: для схемы согласно варианту представить:

Важно: на входах необходимо перебрать всю таблицу истинности, все комбинации входных воздействий; |

ЭН-41 ЭН-42 ЭН-43 |

Задание 3 |

Описание и моделирование последовательностных схем. Задание: для схемы согласно варианту представить:

Важно: необходимо в едином моделировании показать всю таблицу истинности. |

ЭН-41 ЭН-42 ЭН-43 |