Институт интегральной электроники

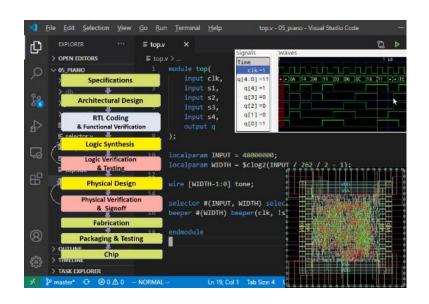

# Лингвистические средства проектирования

Лекция 6

Языки описания аппаратуры. Язык VHDL

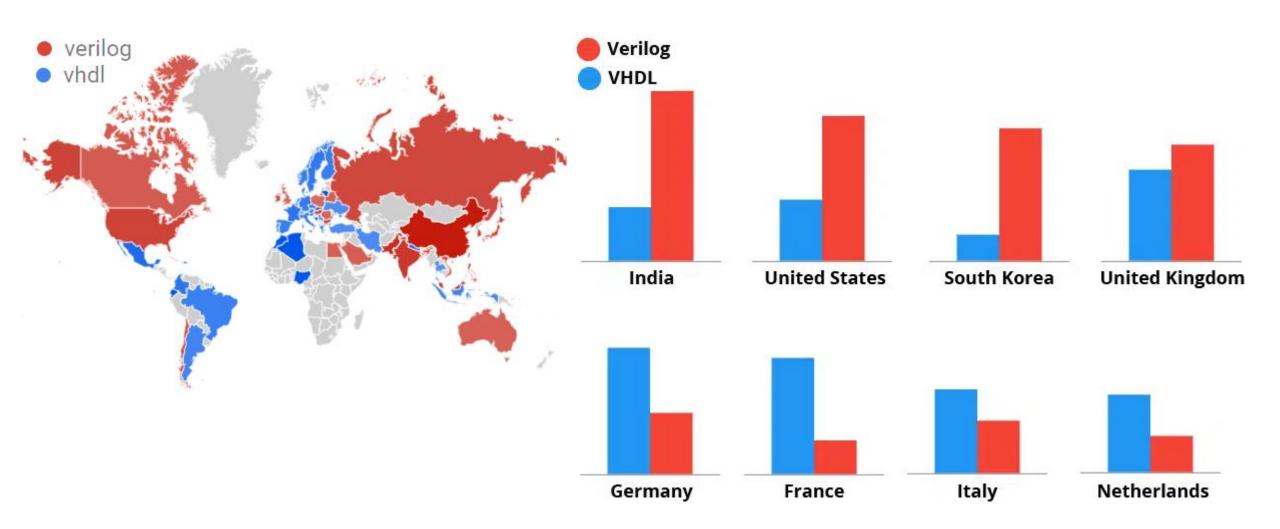

# VHDL - язык разработки в Европе

<sup>\*</sup> https://vhdlwhiz.com/should-i-learn-vhdl-if-verilog-is-becoming-more-popular/

#### Черты языка VHDL

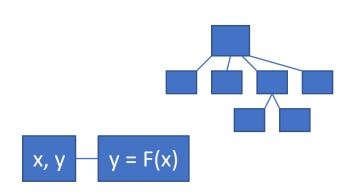

- Поддержка иерархии проектируемые устройства разбиваются на иерархические блоки.

- Описание элемента разделено на интерфейс и архитектурное тело.

- Один объект проектирования может иметь одновременно несколько архитектурных тел.

- Функционирование может быть задано либо с помощью алгоритма, либо с помощью логических функций, либо с помощью указания перечня компонентов и их связей между ними.

- Возможность моделирования параллельно протекающих процессов.

- Возможность проведения временного и функционального моделирования.

- Поддержка пользовательских типов данных.

```

if(X = 1) then

Y <= '0';

else

Y <= '1';

end if;</pre>

```

#### Описание схем на языке VHDL: интерфейс

```

Входы, тип сигнала

```

```

entity inv is

port(x: in bit;

y: out bit);

end inv;

```

Порты устройства, с указанием направлений и передаваемых типов данных

# Описание схем на языке VHDL: архитектурное тело

Функционирование

Имя архитектурного тела какого из элементов описывает

architecture RTL of inv is

begin

y <= not x;

end RTL;

Как функционирует

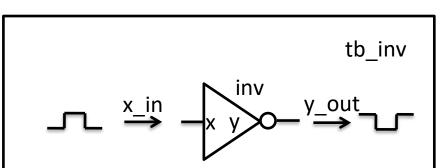

#### Написание тестового окружения

```

entity tb_inv is

end tb_inv;

architecture test of tb_inv is

component inv

port(x: in bit; y: out bit);

end component;

signal x_in, y_out: bit;

begin

p1 : inv port map(x_in, y_out);

p2 : x_in <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns;

end test;

```

## Описание портов устройства: VHDL

```

entity <имя_интерфейса> is

[ generic(<cnucok_napametpob>); ]

[ port(<cnucok_noptob>); ]

[ begin

<типы данных,

entity NAND2 is

значения констант>;

port(x1: in bit; -- первый вход

x2: in bit; -- второй вход

y: out bit -- выход

end [entity] [<имя_интерфейса>];

end NAND2;

entity NAND2 is

port(x1, x2: in bit;

y: out bit);

end NAND2;

```

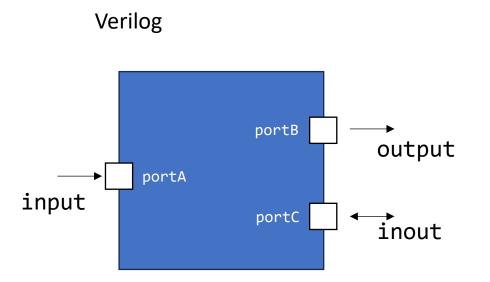

# Направления портов

#### Типы данных портов и сигналов

#### Verilog

```

logic : {

0, -- логический 0

1, -- логическая 1

X, -- неизвестное состояние

Z, -- высокий импеданс

}

```

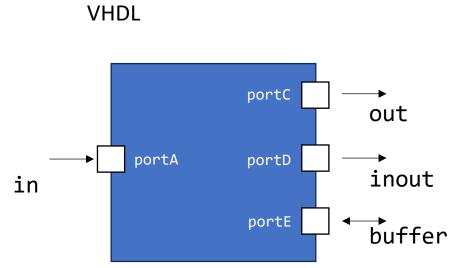

#### **VHDL**

BIT : {'0', '1'};

```

Тип данных bit Tип данных std_logic

```

```

STD_LOGIC : {

'U', -- неинициализированное значение

'Х', -- неизвестное значение

'0', -- логический 0

'1', -- логическая 1

'Z', -- высокий импеданс

'W', -- слабый сигнал, непонятно, он 0 или 1

'L', -- слабый сигнал, подтянутый к 0

'Н', -- слабый сигнал, подтянутый к 1

-- безразличное состояние

```

Тип std\_logic требует подключения библиотеки std\_logic\_1164

```

library ieee;

use ieee.std_logic_1164.all;

```

#### Описание схем с разными типами данных

```

library ieee;

use ieee.std_logic_1164.all;

entity and2 is

port(x1, x2: in std_logic;

y: out std_logic);

end and2;

architecture RTL of and2 is

begin

y \le x1 and x2;

end RTL;

```

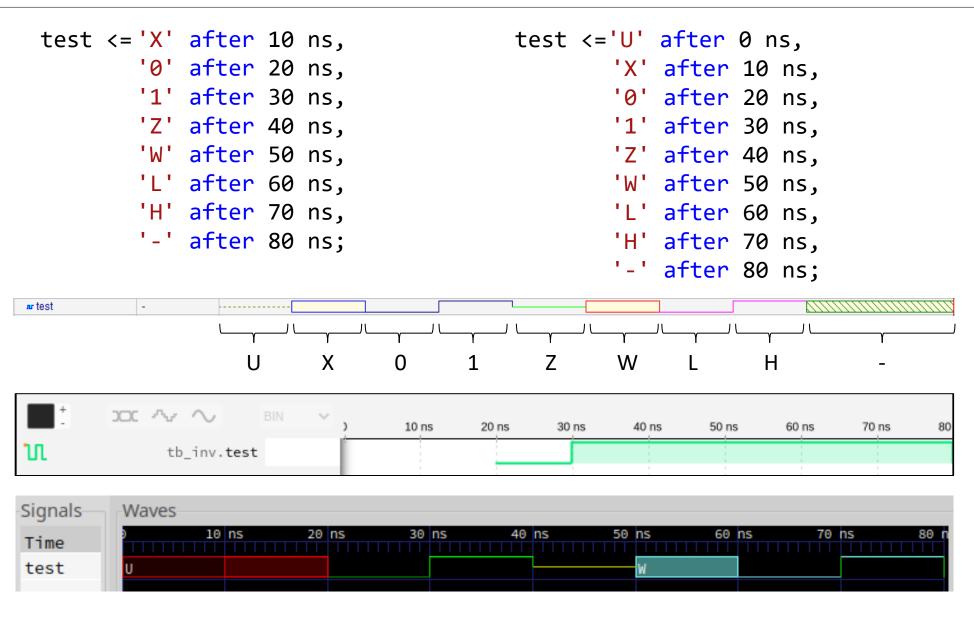

#### Отображение значений сигналов в постпроцессорах

#### Синтаксис описания архитектуры

```

architecture <uмя_apхитектруры> of <uмя_интерфейсa> is

[<cписок_объявлений>;]

begin

<cписок_параллельных_операторов>;

end [architecture] [<имя_apхитектуры>];

```

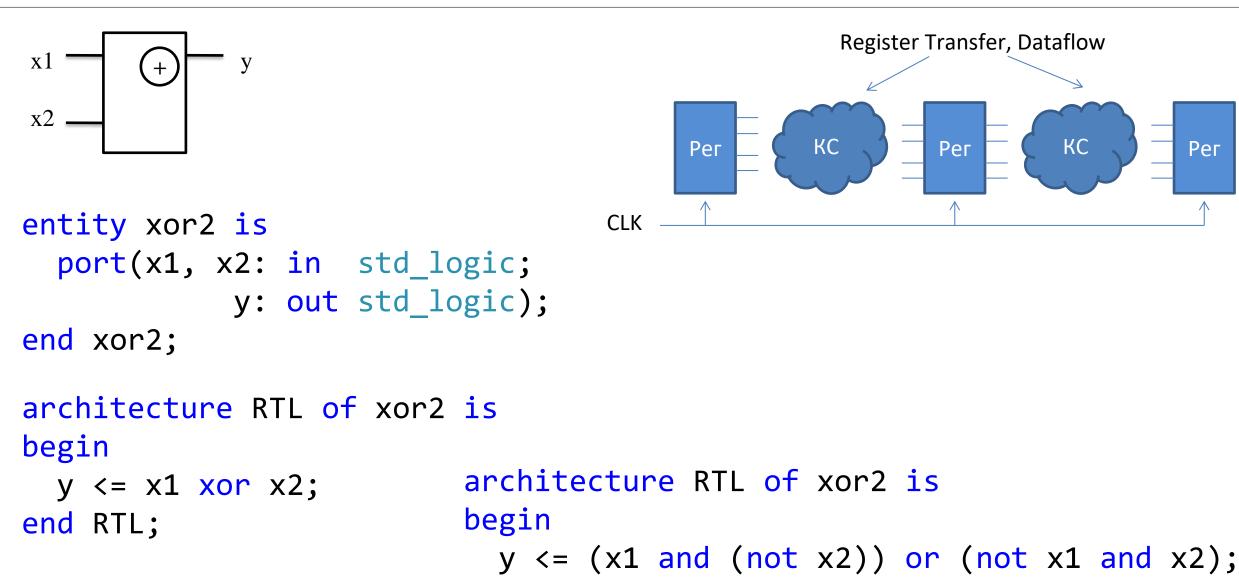

#### Описание архитектурного тела типа RTL

end RTL;

### Этап 1. Проектирование библиотеки элементов

```

library ieee;

use ieee.std_logic_1164.all;

entity inv is

port(x: in std_logic;

y: out std_logic);

end inv;

architecture RTL of inv is

begin

y \le not x;

end RTL;

+ тестовое окружение

```

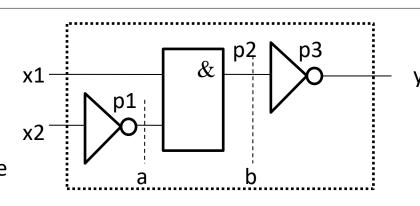

### Этап 2. Описание интерфейса устройства

```

entity DEVICE is

port(x1: in std_logic;

x2: in std_logic;

y: out std_logic);

end DEVICE;

```

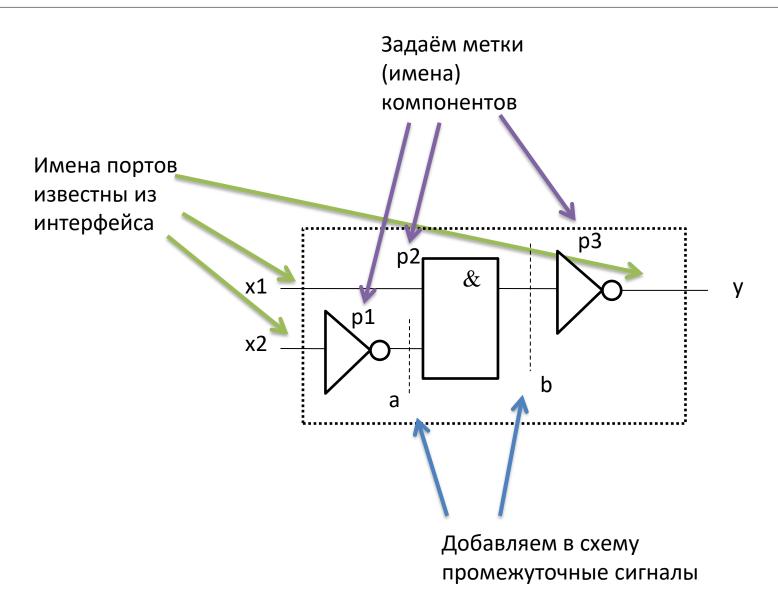

# Этап 3-а. Расстановка недостающих объектов

end STR;

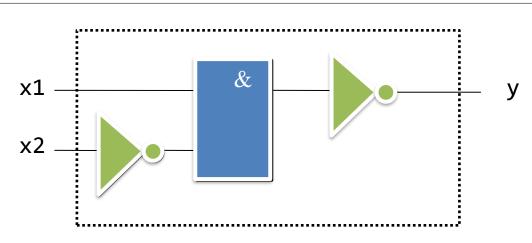

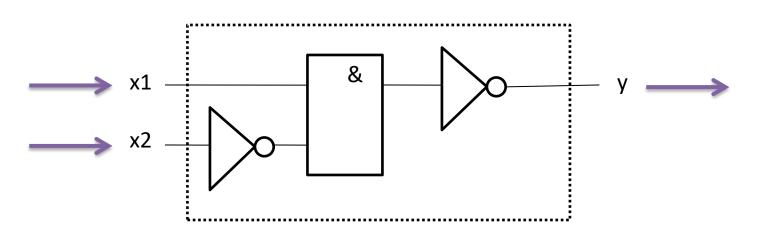

#### Этап 3-б. Описание взаимосвязи компонентов

```

architecture STR of DEVICE is

component inv

port(x: in std_logic;

y: out std_logic);

end component;

component and2

port(x1, x2: in std_logic;

y: out std_logic);

end component;

signal a, b: std_logic;

begin

p1 : inv port map(x2, a);

p2 : and2 port map(x1, a, b);

p3 : inv port map(b, y);

```

Какие из описанных ранее элементов будут использованы?

Перечень недостающих сигналов

Связь элементов посредством сигналов и портов

#### Позиционное и ассоциативное назначение портов

#### Язык Verilog

```

inv i1(x2, a);

inv i1(.x(x2), .y(a));

and2 i2(x1, a, b);

inv i3(b, y);

and2 i2(.x1(x1), .x2(a), .y(b));

inv i3(.x(b), .y(y));

Язык VHDL

i1 : inv port map(x2, a);

i1 : inv port map(x=>x2, y=>a);

i2 : and2 port map(x1, a, b);

i3 : inv port map(b, y);

i2 : and2 port map(x1=>x1, x2=>a, y=>b);

i3 : inv port map(y=>y, x=>b);

```

#### Поведенческое описание схемы на VHDL

| x1 | x2 | у |

|----|----|---|

| 0  | 0  | 1 |

| 0  | 1  | 1 |

| 1  | 0  | 0 |

| 1  | 1  | 1 |

```

entity DEVICE is

port(x1, x2: in std_logic;

y: out std_logic);

end DEVICE;

architecture BEH of DEVICE is

begin

process(x1, x2)

begin

if (x1='1' and x2='0') then

y <= '0';

else

y <= '1';

end if;

end process;

end BEH;

```

# Требования к описанию процессов/процедурных блоков

В процессе обязана быть одна из двух конструкций:

1. список чувствительности;

Без списка чувствительности процесс работает **бесконечно** переходя от одной итерации к другой.

2. оператор ожидания.

Если процесс не содержит ни списка чувствительности, ни оператора ожидания, он **входит в зацикливание**, **моделирование становится невозможным**.

## Формы записи оператора wait

```

wait – оператор ожидания.

4 формы записи оператора:

ожидание в течение определённого времени;

wait for <время>;

2. ожидание изменения сигнала;

wait on <список сигналов>;

3. ожидание выполнения логического условия,

wait until <логическое_условие>;

4. остановка процесса.

wait;

```

#### Формы записи оператора wait: wait for

```

p1: x <= '1' after 0 ns, '0' after 20 ns, '1' after 40 ns, ...

```

```

p1 : process

begin

x <= not x;

wait for 20 ns;

end process;</pre>

```

Аналог в языке Verilog:

```

always

#20 x = ~x;

```

# Пример на wait on

#### AND2

| x2 | x1 | у |

|----|----|---|

| 0  | 0  | 0 |

| 0  | 1  | 0 |

| 1  | 0  | 0 |

| 1  | 1  | 1 |

```

p1 : process

begin

x1 <= not x1;

wait for 20 ns;

end process;

p2 : process

begin

x2 <= not x2;

wait for 40 ns;

end process;

</pre>

always

#40 x = ~x;

end process;

```

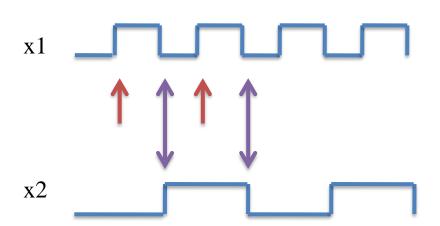

```

p1 : process

begin

x1 <= not x1;

wait for 20 ns;

end process;

p2: process

begin

wait on x1;

wait on x1;

x2 <= not x2;

end process;

```

## Пример на wait until

p1 : process

#### AND2

| x1 | x2 | у |

|----|----|---|

| 0  | 0  | 0 |

| 0  | 1  | 0 |

| 1  | 0  | 0 |

| 1  | 1  | 1 |

```

p1 : process

begin

x1 <= not x1;

wait for 20 ns;

end process;

p2 : process

begin

x2 <= not x2;

wait for 40 ns;

end process;</pre>

```

```

begin

x1 <= not x1;

wait for 20 ns;

end process;

p2 : process

begin

wait until (x1 = '0');

x2 <= not x2;

end process;</pre>

```

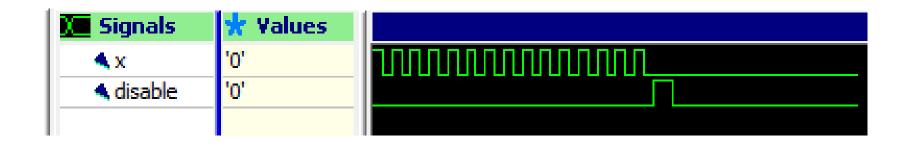

## Остановка процесса: пример на wait;

```

p1 : disable <= '0', '1' after 150 ns, '0' after 160 ns;

p2: process

begin

x \leftarrow not x;

wait for 5 ns;

if (disable = '1') then

wait;

end if;

end process;

```

# Атрибуты сигналов в VHDL

| Имя атрибута             | Назначение атрибута, что возвращает                   |                                                |       |

|--------------------------|-------------------------------------------------------|------------------------------------------------|-------|

| S'stable,<br>S'stable(T) | true, если сигнал не менялся (в течение в             | ремени Т)                                      |       |

| S'event                  | true, если происходит изменение сигнала               |                                                |       |

| S'active                 | true, если была запись, но значение ещё не поменялось |                                                |       |

| S'quiet(T)               | true, если не было обращений в течение                | времени Т                                      |       |

| S'last_value             | предыдущее значение сигнала                           | <pre>process   variable a1, a2: Boolean;</pre> |       |

| S'last_event             | время предыдущего изменения сигнала                   | <pre>begin   Q &lt;= '1' after 10 ns;</pre>    |       |

|                          |                                                       | a1 := Q'active;                                | true  |

|                          |                                                       | a2 := Q'event;                                 | false |

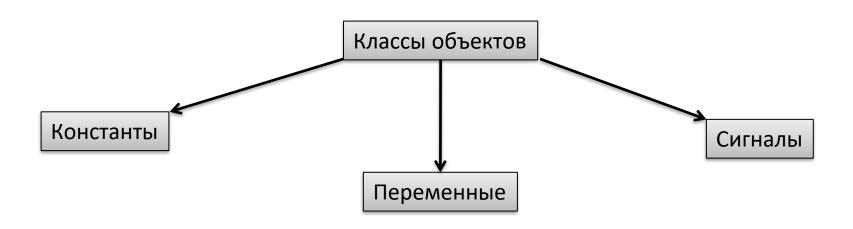

#### Классы объектов в VHDL

```

constant LOGIC_ONE : std_logic := '1';

```

variable TEMP\_VAR : std\_logic := '1';

signal CONNECT : std\_logic := '1';

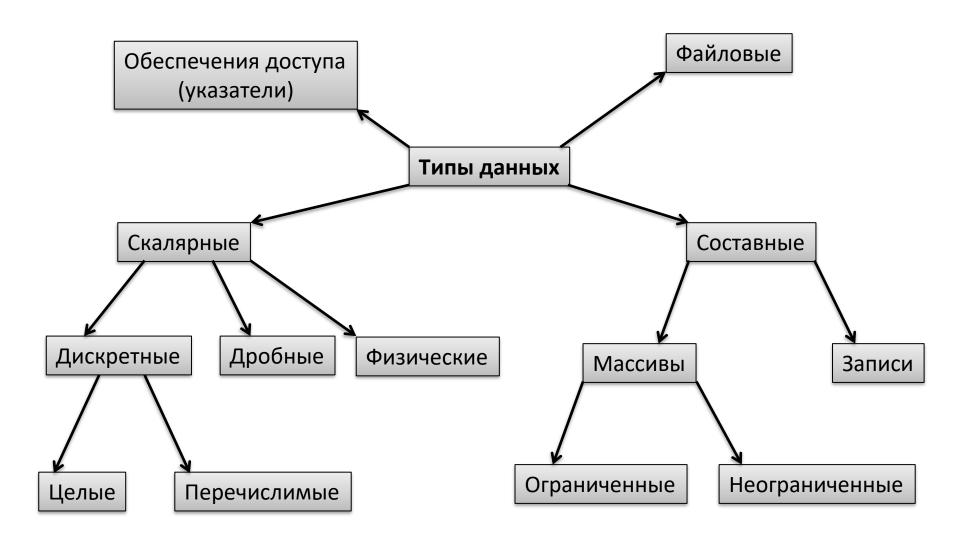

# Типы данных языка VHDL

#### Векторные типы данных (1)

Вектор с типом данных bit:

```

signal x: bit_vector(1 to 8);

Вектор с типом данных std_logic:

library ieee;

ieee.std_logic_1164.all;

use

. . .

signal x: std_logic_vector(1 to 8);

signal x: std_logic_vector(8 downto 1);

signal x: std_logic_vector(10 downto 6);

```

#### Векторные типы данных (2)

```

signal x: std_logic_vector(1 to 8);

```

```

<= "10110101";

x: "10110101";

x(1) <= '0';

x : "00110101";

<= ('1', others => '0');

x: "10000000";

\leftarrow x(5 \text{ to } 8) \& x(1 \text{ to } 4);

x: "00001000";

Χ

<= x(1) & "001100" & '1';

x: "00011001";

Χ

<= (others => '1');

x : "11111111";

X

```

# Атрибуты для работы с массивами

| Имя атрибута | Назначение атрибута               |              | <pre>l_logic_vector(1 t l_logic_vector(4 d</pre> | •            | •          |

|--------------|-----------------------------------|--------------|--------------------------------------------------|--------------|------------|

| A'left       | левая граница массива             | Имя атрибута | Что вернёт                                       | Имя атрибута | Что вернёт |

| A'right      | правая граница массива            | x'left       | 1                                                | y'left       | 4          |

| A'high       | максимальное значение             | x'right      | 4                                                | y'right      | 1          |

| A'low        | диапазона<br>минимальное значение | x'high       | 4                                                | y'high       | 4          |

|              | диапазона                         | x'low        | 1                                                | y'low        | 1          |

| A'range      | диапазон массива                  | x'range      | 1 to 4                                           | y'range      | 4 downto 1 |

| A'length     | длина массива                     | x'length     |                                                  | y'length     |            |

|              |                                   |              | 4                                                |              | 4          |

#### Объявление своих типов и подтипов данных в VHDL

```

INTEGER

от -(2^31 - 1) до +(2^31 - 1)

NATURAL от 0 до +(2^31 - 1)

POSITIVE

от 1 до +(2^31 - 1)

type small_int is range -1023 to 1024;

или

subtype small_int is Integer range -1023 to +1024;

или

variable small_int: Integer is range -1023 to +1024;

```

#### Объявление перечислимых данных в VHDL

```

Перечислимые типы:

type BIT is ('0', '1');

type severity_level is (note, warning, error, failure);

type status is (unknown, idle, work);

Использование перечислимых типов:

signal A: bit;

signal S1: status;

variable B: bit;

variable S2: status;

A <= '1';

A <= idle;

B := '0';

B := work;

```

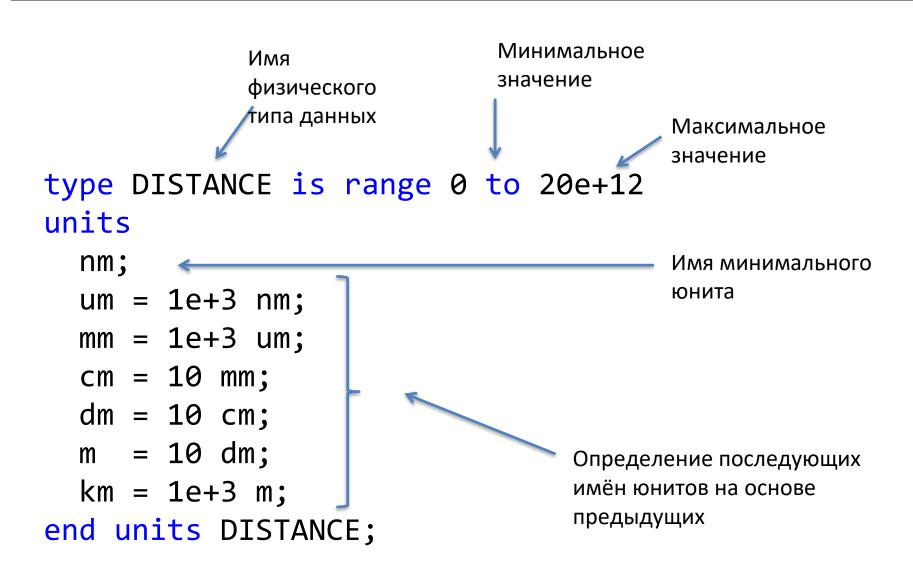

#### Физические типы данных в VHDL

#### Оператор генерации подстановки компонента

```

architecture STR of DEVICE is

component and2

b(1)

a(1)

port(x1, x2: in bit;

y: out bit);

a(2)

end component;

component inv

a(3)

b(2)

port(x: in bit;

y: out bit);

a(4)

end component;

a(5)

b(3)

signal a: bit_vector(1 to 9);

a(6)

signal b: bit vector(1 to 5);

begin

a(7)

b(4)

g1: for i in 1 to 4 generate

a(8)

p1: and2 port map(a(i*2-1), a(i*2), b(i));

end generate;

p2: inv port map(a(9), b(5));

end STR;

```

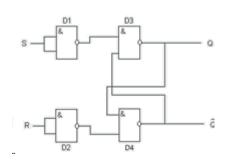

#### Конфигурации в языке VHDL

```

entity tb device is

architecture TEST of tb device is

end tb_device;

component DEVICE

begin

p1 : DEVICE port map ...

p2 : DEVICE port map ...

p3 : DEVICE port map ...

end TEST;

configuration config1 of tb device is

for TEST

for p1 : DEVICE use entity work.DEVICE(STR); end for;

for p2 : DEVICE use entity work.DEVICE(RTL); end for;

for p3 : DEVICE use entity work.DEVICE(BEH); end for;

end for;

end configuration;

```

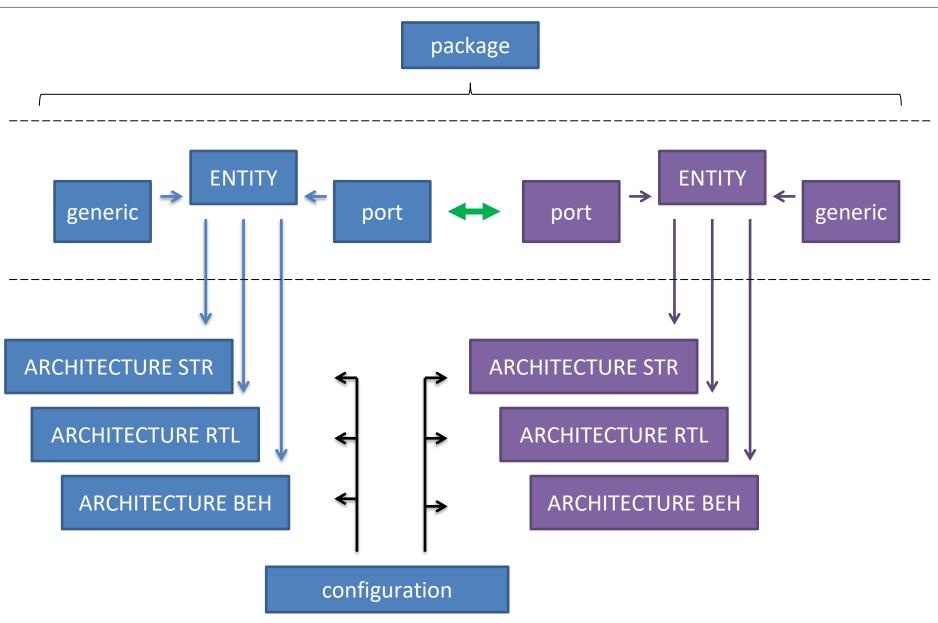

# Архитектура дизайна в языке VHDL

# Запуск симулятора GHDL

ghdl -a adder.vhd

ghdl -a tb\_adder.vhd

ghdl -r tb\_adder --vcd=adder.vcd --stop-time=100ns

### Библиотека SystemC для C++

**}**;

```

entity inv is

module inv(x, y);

SC_MODULE(inv) {

port(x: in bit;

y: out bit);

input x;

sc in <bool> x;

sc_out<bool> y;

end inv;

output y;

architecture BEH of inv is

always@(x)

void operate() {

y.write(!x.read());

begin

y = \sim x;

process(x)

endmodule

begin

SC CTOR(inv) {

y \le not x;

SC_METHOD(operate);

end process;

end RTL;

sensitive << x;</pre>

```

#### Модуль MyHDL для Python

```

@block

def inv(x, y):

@always(x)

def logic():

y.next = not x

return logic

@block

def and2(x1, x2, y):

@always(x1, x2)

def logic():

y.next = x1 & x2

return logic

```

```

@block

def dff(q, d, clk):

@always(clk.posedge)

def logic():

q.next = d

return logic

```